## UltraSPARC T1<sup>TM</sup> Supplement to the *UltraSPARC Architecture* 2005

Draft D2.0, 17 Mar 2006

Privilege Levels: Privileged and Nonprivileged

Distribution: Public

Sun Microsystems, Inc. 4150 Network Circle Santa Clara, CA 95054 U.S.A. 650-960-1300

Part No: 819-3404-04 Revision: Draft D2.0, 17 Mar 2006 Copyright 2002-2006 Sun Microsystems, Inc., 4150 Network Circle • Santa Clara, CA 950540 USA. All rights reserved.

This product or document is protected by copyright and distributed under licenses restricting its use, copying, distribution, and decompilation. No part of this product or document may be reproduced in any form by any means without prior written authorization of Sun and its licensors, if any. Third-party software, including font technology, is copyrighted and licensed from Sun suppliers.

Parts of the product may be derived from Berkeley BSD systems, licensed from the University of California. UNIX is a registered trademark in the U.S. and other countries, exclusively licensed through X/Open Company, Ltd. For Netscape Communicator™, the following notice applies: Copyright 1995 Netscape Communications Corporation. All rights reserved.

Sun, Sun Microsystems, the Sun logo, Solaris, and VIS are trademarks, registered trademarks, or service marks of Sun Microsystems, Inc. in the U.S. and other countries. All SPARC trademarks are used under license and are trademarks or registered trademarks of SPARC International, Inc. in the U.S. and other countries. Products bearing SPARC trademarks are based upon an architecture developed by Sun Microsystems, Inc.

The OPEN LOOK and Sun<sup>TM</sup> Graphical User Interface was developed by Sun Microsystems, Inc. for its users and licensees. Sun acknowledges the pioneering efforts of Xerox in researching and developing the concept of visual or graphical user interfaces for the computer industry. Sun holds a non-exclusive license from Xerox to the Xerox Graphical User Interface, which license also covers Sun's licensees who implement OPEN LOOK GUIs and otherwise comply with Sun's written license agreements.

**RESTRICTED RIGHTS**: Use, duplication, or disclosure by the U.S. Government is subject to restrictions of FAR 52.227-14(g)(2)(6/87) and FAR 52.227-19(6/87), or DFAR 252.227-7015(b)(6/95) and DFAR 227.7202-3(a).

DOCUMENTATION IS PROVIDED "AS IS" AND ALL EXPRESS OR IMPLIED CONDITIONS, REPRESENTATIONS AND WARRANTIES, INCLUDING ANY IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT, ARE DISCLAIMED, EXCEPT TO THE EXTENT THAT SUCH DISCLAIMERS ARE HELD TO BE LEGALLY INVALID.

Copyright 2002–2006 Sun Microsystems, Inc., 4150 Network Circle • Santa Clara, CA 950540 Etats-Unis. Tous droits réservés.

Des parties de ce document est protégé par un copyright© 1994 SPARC International, Inc.

Ce produit ou document est protégé par un copyright et distribué avec des licences qui en restreignent l'utilisation, la copie, la distribution, et la décompilation. Aucune partie de ce produit ou document ne peut être reproduite sous aucune forme, par quelque moyen que ce soit, sans l'autorisation préalable et écrite de Sun et de ses bailleurs de licence, s'il y en a. Le logiciel détenu par des tiers, et qui comprend la technologie relative aux polices de caractères, est protégé par un copyright et licencié par des fournisseurs de Sun.

Sun, Sun Microsystems, le logo Sun, Solaris, et VIS sont des marques de fabrique ou des marques déposées, ou marques de service, de Sun Microsystems, Inc. aux Etats-Unis et dans d'autres pays. Toutes les marques SPARC sont utilisées sous licence et sont des marques de fabrique ou des marques déposées de SPARC International, Inc. aux Etats-Unis et dans d'autres pays. Les produits portant les marques SPARC sont basés sur une architecture développée par Sun Microsystems, Inc.

L'interface d'utilisation graphique OPEN LOOK et Sun™ a été développée par Sun Microsystems, Inc. pour ses utilisateurs et licenciés. Sun reconnaît les efforts de pionniers de Xerox pour la recherche et le développement du concept des interfaces d'utilisation visuelle ou graphique pour l'industrie de l'informatique. Sun détient une licence non exclusive de Xerox sur l'interface d'utilisation graphique Xerox, cette licence couvrant également les licenciés de Sun qui mettent en place l'interface d'utilisation graphique OPEN LOOK et qui en outre se conforment aux licences écrites de Sun.

CETTE PUBLICATION EST FOURNIE "EN L'ETAT" ET AUCUNE GARANTIE, EXPRESSE OU IMPLICITE, N'EST ACCORDEE, Y COMPRIS DES GARANTIES CONCERNANT LA VALEUR MARCHANDE, L'APTITUDE DE LA PUBLICATION A REPONDRE A UNE UTILISATION PARTICULIERE, OU LE FAIT QU'ELLE NE SOIT PAS CONTREFAISANTE DE PRODUIT DE TIERS. CE DENI DE GARANTIE NE S'APPLIQUERAIT PAS, DANS LA MESURE OU IL SERAIT TENU JURIDIQUEMENT NUL ET NON AVENU.

Comments and "bug reports" regarding this document are welcome; they should be submitted to email address: UST1-editor@sun.com

## Contents

| 1 | Ultr | aSPARC T1 Basics                                |

|---|------|-------------------------------------------------|

|   | 1.1  | Background                                      |

|   | 1.2  | UltraSPARC T1 Overview                          |

|   | 1.3  | UltraSPARC T1 Components                        |

|   |      | 1.3.1 SPARC Physical Core                       |

|   |      | 1.3.2 Floating-Point Unit (FPU)                 |

|   |      | 1.3.3 L2 Cache                                  |

| 2 | Data | a Formats                                       |

| 3 | Reg  | isters                                          |

|   | 3.1  | Ancillary State Registers (ASRs)                |

|   |      | 3.1.1 TICK Register                             |

|   |      | 3.1.2 General Status Register (GSR)             |

|   |      | 3.1.3 Software Interrupt Register (SOFTINT)     |

|   |      | 3.1.4 Tick Compare Register (TICK_CMPR)         |

|   |      | 3.1.5 System Tick Register (STICK)              |

|   |      | 3.1.6 System Tick Compare Register (STICK_CMPR) |

|   |      | 3.1.7 PCR and PIC Registers                     |

|   | 3.2  | PR State Registers                              |

|   |      | 3.2.1 Trap State (TSTATE)                       |

|   |      | 3.2.2 Processor State Register (PSTATE)         |

|   |      | 3.2.3 Trap Level Register (TL)                  |

|   |      | 3.2.4 Global Level Register (GL)                |

|   | 3.3  | Floating-Point State Register (FSR)             |

| 4 | Inst | ruction Set Overview                            |

|   | 4.1  | State Register Access                           |

|    | 4.2   | Floating-P     | oint Operate (FPop) Instructions             | 11 |

|----|-------|----------------|----------------------------------------------|----|

|    | 4.3   | Reserved (     | Opcodes and Instruction Fields               | 12 |

|    | 4.4   | Register W     | Vindow Management                            | 12 |

| 5  | Inst  | ruction Def    | initions                                     | 13 |

|    | 5.1   | Instruction    | n Set Summary                                | 13 |

|    | 5.2   | Prefetch a     | nd Prefetch from Alternate Space             | 16 |

|    | 5.3   | Trap on In     | teger Condition Codes (Tcc)                  | 16 |

|    | 5.4   | VIS Instru     | ctions                                       | 16 |

|    | 5.5   | Partitioned    | d Add/Subtract Instructions                  | 17 |

|    | 5.6   | 0              | a                                            |    |

|    | 5.7   | -              | Logical Operate Instructions                 |    |

|    | 5.8   | Block Load     | d and Store Instructions.                    | 18 |

| 6  | Trap  | s              |                                              | 29 |

|    | 6.1   | Trap Level     | ls                                           | 29 |

| 7  | Inte  | rrunt Hand     | ling                                         |    |

|    | 11100 | 7.0.1          | Interrupt Queue Registers                    |    |

| 0  |       | 71011          |                                              |    |

| 8  |       | 5              | s                                            |    |

|    | 8.1   |                |                                              |    |

|    | 8.2   |                | Memory Models                                |    |

|    |       | 8.2.1<br>8.2.2 | Total Store Order.      Relaxed Memory Order |    |

| •  |       |                |                                              |    |

| 9  |       |                | and ASIs                                     |    |

|    | 9.1   |                | paces                                        |    |

|    |       | 9.1.1<br>9.1.2 | Access to Nonexistent Memory or I/O          |    |

|    | 9.2   |                | Address Spaces                               |    |

|    | .2    | 9.2.1          | ASI_REAL and ASI_REAL_LITTLE                 |    |

|    |       | 9.2.2          | ASI_REAL_IO and ASI_REAL_IO_LITTLE           |    |

|    |       | 9.2.3          | ASI_SCRATCHPAD                               | 46 |

| 10 | Perf  | ormance In     | strumentation                                |    |

|    | 10.1  | Performan      | ce Control Register                          | 49 |

|    |       |                | rformance Instrumentation Counter            |    |

| 11 | Men   | norv Manag     | gement                                       | 53 |

|    | 11.1  |                | n Table Entry (TTE)                          |    |

|    |       | 11.1.1         | TTE Tag Format                               |    |

|    |       | 11.1.2         | TTE Data Format                              |    |

|    | 11.2 | Translatio       | n Storage Buffer55                                                                |

|----|------|------------------|-----------------------------------------------------------------------------------|

|    | 11.3 | MMU-Rel          | ated Faults and Traps57                                                           |

| 12 | Imp  | lementatio       | n Dependencies                                                                    |

|    | 12.1 | SPARC V9         | 9 General Information                                                             |

|    |      | 12.1.1           | Level-2 Compliance (Impl. Dep. #1)                                                |

|    |      | 12.1.2           | Unimplemented Opcodes, ASIs, and ILLTRAP 59                                       |

|    |      | 12.1.3           | Trap Levels (Imp. Dep. #37, 38, 39, 40, 101, 114, 115) 59                         |

|    |      | 12.1.4           | Trap Handling (Imp. Dep. #16, 32, 33, 35, 36, 44) 60                              |

|    |      | 12.1.5           | Population Count Instruction (POPC) 60                                            |

|    |      | 12.1.6           | Secure Software                                                                   |

|    |      | 12.1.7           | Address Masking (Impl. Dep. #125) 60                                              |

|    | 12.2 |                  | 9 Integer Operations61                                                            |

|    |      | 12.2.1           | Integer Register File and Window Control Registers (Impl. Dep. #2) 61             |

|    |      | 12.2.2           | SAVE Instruction                                                                  |

|    |      | 12.2.3           | Clean Window Handling (Impl. Dep. #102) 62                                        |

|    |      | 12.2.4           | Integer Multiply and Divide                                                       |

|    |      | 12.2.5           | MULScc                                                                            |

|    | 12.3 |                  | PFloating-Point Operations                                                        |

|    |      | 12.3.1           | Subnormal Operands and Results: Nonstandard Operation 62                          |

|    |      | 12.3.2           | Overflow, Underflow, and Inexact Traps (Impl. Dep. #3, 55) 63                     |

|    |      | 12.3.3           | Quad-Precision Floating-Point Operations (Impl. Dep. #3). 63                      |

|    |      | 12.3.4<br>12.3.5 | Floating-Point Square Root                                                        |

|    |      | 12.3.3           | 64                                                                                |

|    |      | 12.3.6           | Floating-Point State Register (FSR) (Impl. Dep. #13, 19, 22, 23, 24) 65           |

|    | 12.4 | SPARC V9         | Memory-Related Operations67                                                       |

|    |      | 12.4.1           | Load/Store Alternate Address Space (Impl. Dep. #5, 29, 30) 67                     |

|    |      | 12.4.2           | Read/Write ASR (Impl. Dep. #6, 7, 8, 9, 47, 48)                                   |

|    |      | 12.4.3           | FLUSH and Self-Modifying Code (Impl. Dep. #122) 67                                |

|    |      | 12.4.4           | PREFETCH{A} (Impl. Dep. #103, 117) 68                                             |

|    |      | 12.4.5           | Instruction Prefetch                                                              |

|    |      | 12.4.6           | LDTW/STTW Handling (Impl. Dep. #107, 108)                                         |

|    |      | 12.4.7           | Floating-Point <i>mem_address_not_aligned</i> (Impl. Dep. #109, 110, 111, 112) 69 |

|    |      | 12.4.8           | Supported Memory Models (Impl. Dep. #113, 121) 69                                 |

|    |      | 12.4.9           | Implicit ASI when $TL > 0$ (Impl. Dep. #124)                                      |

|    | 12.5 |                  | RC V9 Extensions70                                                                |

|    |      | 12.5.1           | Cache Subsystem                                                                   |

|    |      | 12.5.2           | Block Memory Operations                                                           |

|    |      | 12.5.3           | Partial Stores                                                                    |

٠

|   | 12.5.4 Short Floating-Point Loads and Stores                         |

|---|----------------------------------------------------------------------|

|   | 12.5.5 Interrupt Vector Handling                                     |

|   | 12.5.6 Power-Down Support                                            |

|   | 12.5.7 UltraSPARC T1 Instruction Set Extensions (Impl. Dep. #106) 71 |

|   | 12.5.8 Performance Instrumentation                                   |

| Α | Assembly Language Syntax                                             |

| B | Programming Guidelines                                               |

|   | B.1 Multithreading75                                                 |

|   | B.2 Pipeline Strand Flush                                            |

|   | B.3 Instruction Latencies                                            |

|   | B.4 Grouping Rules                                                   |

|   | B.5 Floating-Point Operations                                        |

|   | B.6 Synchronization                                                  |

| ~ |                                                                      |

| C | Opcode Maps93                                                        |

| D | Instructions and Exceptions 103                                      |

| Ε | IEEE 754 Floating Point Support 105                                  |

|   | E.1 Special Operand Handling105                                      |

|   | E.1.1 Infinity Arithmetic 106                                        |

|   | E.1.2 Zero Arithmetic 111                                            |

|   | E.1.3 NaN Arithmetic 112                                             |

|   | E.1.4 Special Inexact Exceptions 113                                 |

|   | E.2 Subnormal Handling 114                                           |

| F | Caches and Cache Coherency 115                                       |

|   | F.1 Cache Flushing                                                   |

|   | F.1.1 Displacement Flushing 116                                      |

|   | F.1.2 Memory Accesses and Cacheability                               |

|   | F.1.3 Coherence Domains 117                                          |

|   | F.1.4 Memory Synchronization: MEMBAR and FLUSH 119                   |

|   | F.1.5 Atomic Operations 120                                          |

|   | F.1.6 Nonfaulting Load 121                                           |

| G | Glossary                                                             |

|   |                                                                      |

|   | Index                                                                |

## Preface

Welcome to the UltraSPARC T1 Processor Supplement, D2.0. This document contains information about the processor-specific aspects of the architecture and programming of the UltraSPARC T1 processor, one of Sun Microsystems' family processors compliant with UltraSPARC Architecture<sup>TM</sup>. It is intended to supplement the *UltraSPARC Architecture* 2005 with processor-specific information.

#### **Target Audience**

This User's Guide is mainly targeted for programmers who write software for the UltraSPARC T1 processor. This manual contains a depository of information that is useful to operating system programmers, application software programmers and logic designers, who are trying to understand the architecture and operation of the UltraSPARC T1 processor. This manual is both a guide and a reference manual for programming of the processor.

## Fonts and Notational Conventions

Fonts are used as follows:

- *Italic* font is used for emphasis, book titles, and the first instance of a word that is defined.

- *Italic* font is also used for terms where substitution is expected, for example, "fccn", "virtual processor n", or "reg\_plus\_imm".

- Italic sans serif font is used for exception and trap names. For example, "The privileged\_action exception...."

- Iowercase helvetica font is used for register field names (named bits) and instruction field names, for example: "The rs1 field contains...."

- UPPERCASE HELVETICA font is used for register names; for example, FSR.

- TYPEWRITER (Courier) font is used for literal values, such as code (assembly language, C language, ASI names) and for state names. For example: %f0, ASI\_PRIMARY, execute\_state.

- When a register field is shown along with its containing register name, they are separated by a period ('.'), for example, FSR.cexc.

- UPPERCASE words are acronyms or instruction names. Some common acronyms appear in the glossary. Note: Names of some instructions contain both upper- and lower-case letters.

- An underscore character joins words in register, register field, exception, and trap names. **Note:** Such words may be split across lines at the underbar without an intervening hyphen. For example: "This is true whenever the integer\_condition\_ code field...."

The following notational conventions are used:

- The left arrow symbol (  $\leftarrow$  ) is the assignment operator. For example, "PC  $\leftarrow$  PC + 1" means that the Program Counter (PC) is incremented by 1.

- Square brackets ([]) are used in two different ways, distinguishable by the context in which they are used:

- Square brackets indicate indexing into an array. For example, TT[TL] means the element of the Trap Type (TT) array, as indexed by the contents of the Trap Level (TL) register.

- Square brackets are also used to indicate optional additions/extensions to symbol names. For example, "ST[D,Q]F" expands to all three of "STF", "STDF", and "STQF". Similarly, ASI\_PRIMARY[\_LITTLE] indicates two related address space identifiers, ASI\_PRIMARY and ASI\_PRIMARY\_LITTLE. (Contrast with the use of angle brackets, below)

- Angle brackets ( <> ) indicate mandatory additions/extensions to symbol names. For example, "ST<D|Q>F" expands to mean "STDF" and "STQF". (Contrast with the second use of square brackets, above)

- Curly braces ( { } ) indicate a bit field within a register or instruction. For example, CCR{4} refers to bit 4 in the Condition Code Register.

- A consecutive set of values is indicated by specifying the upper and lower limit of the set separated by a colon (:), for example, CCR{3:0} refers to the set of four least significant bits of register CCR. (Contrast with the use of double periods, below)

- A double period (..) indicates any *single* intermediate value between two given end values is possible. For example, NAME[2..0] indicates four forms of NAME exist: NAME, NAME2, NAME1, and NAME0; whereas NAME<2..0> indicates that three forms exist: NAME2, NAME1, and NAME0. (Contrast with the use of the colon, above)

- A vertical bar ( | ) separates mutually exclusive alternatives inside square brackets ([]), angle brackets ( < > ), or curly braces ( { } ). For example, "NAME[A | B]" expands to "NAME, NAMEA, NAMEB" and "NAME<A | B>" expands to "NAMEA, NAMEB".

- The asterisk (\*) is used as a wild card, encompassing the full set of valid values. For example, FCMP\* refers to FCMP with all valid suffixes (in this case, FCMP<s|d|q> and FCMPE<s|d|q>). An asterisk is typically used when the full list of valid values either is not worth listing (because it has little or no relevance in the given context) or the valid values are too numerous to list in the available space.

- The slash ( / ) is used to separate paired or complementary values in a list, for example, "the LDBLOCKF/STBLOCKF instruction pair ...."

- The double colon (::) is an operator that indicates concatenation (typically, of bit vectors). Concatenation strictly strings the specified component values into a single longer string, in the order specified. The concatenation operator performs no arithmetic operation on any of the component values.

## Notation for Numbers

Numbers throughout this specification are decimal (base-10) unless otherwise indicated. Numbers in other bases are followed by a numeric subscript indicating their base (for example,  $1001_2$ , FFFF  $0000_{16}$ ). In some cases, numbers may be preceded by "0x" to indicate hexadecimal (base-16) notation (for example, 0xFFFF 0000). Long binary and hexadecimal numbers within the text may have spaces inserted every four characters to improve readability.

An en dash ( – ) with no spaces indicates a range, for example,  $0001_{16}$ - $0000_{16}$ .

Also see the colon ( : ) and double period (  $\dots$  ) notation described in the previous section.

#### Informational Notes

This manual provides several different types of information in notes, as follows:

**Note** General notes contain incidental information relevant to the paragraph preceding the note.

| Programming<br>Note    | Programming notes contain incidental information about how software can use an architectural feature.                                                                                             |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Implementation<br>Note | An Implementation Note contains incidental information,<br>describing how an UltraSPARC Architecture processor might<br>implement an architectural feature.                                       |

|                        | Note containing information about possible differences between<br>UltraSPARC Architecture and SPARC V9 implementations. Such<br>information may not pertain to other SPARC V9<br>implementations. |

## UltraSPARC T1 Basics

## 1.1 Background

UltraSPARC T1 is the first chip multiprocessor that fully implements Sun's Throughput Computing initiative. Throughput Computing is a technique that takes advantage of the thread-level parallelism that is present in most commercial workloads. Unlike desktop workloads, which often have a small number of threads concurrently running, most commercial workloads achieve their scalability by employing large pools of concurrent threads.

Historically, microprocessors have been designed to target desktop workloads, and as a result have focused on running a single thread as quickly as possible. Single thread performance is achieved in these microprocessors by a combination of extremely deep pipelines (over 20 stages in Pentium 4) and by executing multiple instructions in parallel (referred to as instruction-level parallelism, or ILP). The basic tenet behind Throughput Computing is that exploiting ILP and deep pipelining has reached the point of diminishing returns and as a result, current microprocessors do not utilize their underlying hardware very efficiently.

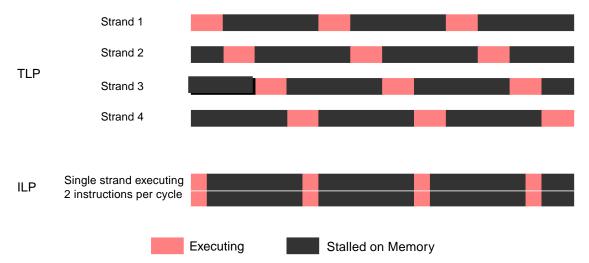

For many commercial workloads, the physical processor core will be idle most of the time waiting on memory, and even when it is executing it will often be able to only utilize a small fraction of its wide execution width. So rather than building a large and complex ILP processor that sits idle most of the time, a number of small, single-issue physical processor cores that employ multithreading are built in the same chip area. Combining multiple physical processors cores on a single chip with multiple hardware-supported threads (strands) per physical processor core, allows very high performance for highly threaded commercial applications. This approach is called thread-level parallelism (TLP). The difference between TLP and ILP is shown in FIGURE 1-1.

FIGURE 1-1 Differences Between TLP and ILP

The memory stall time of one strand can often be overlapped with execution of other strands on the same physical processor core, and multiple physical processor cores run their strands in parallel. In the ideal case, shown in FIGURE 1-1, memory latency can be completely overlapped with execution of other strands. In contrast, instruction-level parallelism simply shortens the time to execute instructions, and does not help much in overlapping execution with memory latency.<sup>1</sup>

Given this ability to overlap execution with memory latency, why don't more processors utilize TLP? The answer is that designing processors is a mostly evolutionary process, and the ubiquitous deeply pipelined, wide ILP physical processor cores of today are the evolutionary outgrowth from a time when the CPU was the bottleneck in delivering good performance.

With physical processor cores capable of multiple-GHz clocking, the performance bottleneck has shifted to the memory and I/O subsystems and TLP has an obvious advantage over ILP for tolerating the large I/O and memory latency prevalent in commercial applications. Of course, every architectural technique has its advantages and disadvantages. The one disadvantage of employing TLP over ILP is that execution of a single strand may be slower on a TLP processor than an ILP processor. With physical processor cores running at frequencies well over one GHz, a strand capable of executing only a single instruction per cycle is fully capable of completing tasks in the time required by the application, making this disadvantage a non-issue for nearly all commercial applications.

<sup>&</sup>lt;sup>1.</sup> Processors that employ out-of-order ILP can overlap some memory latency with execution. However, this overlap is typically limited to shorter memory latency events such as L1 cache misses that hit in the L2 cache. Longer memory latency events such as main memory accesses are rarely overlapped to a significant degree with execution by an out-of-order processor.

## 1.2 UltraSPARC T1 Overview

UltraSPARC T1 is a single-chip multiprocessor. UltraSPARC T1 contains eight SPARC® physical processor cores. Each SPARC physical processor core has full hardware support for four virtual processors (or "strands"). These four strands run simultaneously, with the instructions from each of the four strands executed round-robin by the single-issue pipeline. When a strand encounters a long-latency event, such as a cache miss, it is marked unavailable and instructions will not be issued from that strand until the long-latency event is resolved. Round-robin execution of the remaining available strands will continue while the long-latency event of the first strand is resolved.

Each SPARC physical core has a 16-Kbyte, 4-way associative instruction cache (32byte lines), and 8K-byte, 4-way associative data cache (16-byte lines) that are shared by the four strands. The eight SPARC physical cores are connected through a crossbar to an on-chip unified 3-Mbyte, 12-way associative L2 cache (with 64-byte lines). The L2 cache is banked 4 ways to provide sufficient bandwidth for the eight SPARC physical cores.

## 1.3 UltraSPARC T1 Components

This section describes each component in UltraSPARC T1:

- SPARC physical core

- Floating-point unit

- L2 cache

#### 1.3.1 SPARC Physical Core

Each SPARC physical core has hardware support for four strands. This support consists of a full register file (with eight register windows) per strand, with most of the ASI, ASR, and privileged registers replicated per strand. The four strands share the instruction and data caches.

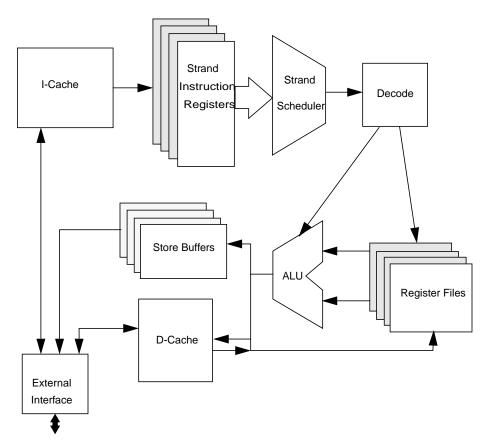

FIGURE 1-2 illustrates SPARC physical core.

FIGURE 1-2 SPARC Core Block Diagram

#### 1.3.2 Floating-Point Unit (FPU)

A single floating-point unit is shared by all eight SPARC physical cores. The shared floating-point unit is sufficient for most commercial applications, in which fewer than 1% of instructions typically involve floating-point operations.

#### 1.3.3 L2 Cache

The L2 cache is banked four ways, with the bank selection based on address bits 7:6. The cache is 3 Mbytes, 12-way set associative, and has a line size of 64 bytes.

## Data Formats

The UltraSPARC T1 processor supports all UltraSPARC Architecture 2005 data formats; see the Data Formats chapter of the *UltraSPARC Architecture* 2005 for details.

## Registers

This chapter discusses the specifics of UltraSPARC T1 registers, as they differ from the register definitions in *UltraSPARC Architecture* 2005.

## 3.1 Ancillary State Registers (ASRs)

#### 3.1.1 TICK Register

See the UltraSPARC Architecture 2005 for a general description of this register.

The TICK register contains two fields: npt and counter. On an UltraSPARC T1 processor, the npt field is replicated per strand, while the counter field is shared by all four strands on a physical processor core. The counter increments each physical processor core clock but, on an UltraSPARC T1 processor, the least significant 2 bits of the counter field always read as 0.

#### 3.1.2 General Status Register (GSR)

Each strand has a nonprivileged General Status register (GSR), as described in the *UltraSPARC Architecture* 2005.

All UltraSPARC Architecture 2005 **GSR** fields are supported in the UltraSPARC T1 implementation. However, the **mask** and **scale** fields are not directly written by VIS instructions; they are provided for use by software emulation.

#### 3.1.3 Software Interrupt Register (SOFTINT)

Each strand has a privileged software interrupt register, as described in the *UltraSPARC Architecture* 2005.

The software interrupt register contains three fields: sm, int\_level, and tm. Setting any of sm, tm, or SOFTINT{14} generates an *interrupt\_level\_14* exception. However, these bits are considered completely independent of each other. Thus, a Stick Compare event will only set bit 16 and generate *interrupt\_level\_14* exception, not also set bit 14.

| UltraSPARC T1 | It is possible (but difficult) in UltraSPARC T1 for software to        |

|---------------|------------------------------------------------------------------------|

| Programming   | clear a SOFTINT bit between the setting of that bit and the            |

| Note          | generation of the interrupt from the bit being set because (there      |

|               | is a three-cycle window between the setting of the bit and the         |

|               | interrupt in UltraSPARC T1). If software were to do this, it           |

|               | would see an <i>interrupt_level_n</i> interrupt, but would find no bit |

|               | set in the SOFTINT register. Note that normal software would           |

|               | only clear a bit in response to taking the <i>interrupt_level_n</i>    |

|               | exception, so this race condition should not occur in normal           |

|               | operation.                                                             |

**UltraSPARC T1 Programming Note** It is possible, but even more difficult than the above case, for software to zero a SOFTINT bit as it is getting set to 1, while another core is accessing its SOFTINT register, with timing such that hardware decides to take a SOFTINT trap, but the SOFTINT register is clear by the time it decides the trap number. In this case, hardware will take a trap 40<sub>16</sub>. Since software should only clear a bit that is known to be set, this should never happen in normal operation.

#### 3.1.4 Tick Compare Register (TICK\_CMPR)

Each strand has a privileged Tick Compare (TICK\_CMPR) register, as described in the *UltraSPARC Architecture* 2005.

#### 3.1.5 System Tick Register (STICK)

On an UltraSPARC T1 processor, the STICK register is an alias for the TICK register. Writes to STICK will be reflected in TICK, and vice versa. See the description of TICK above for the behavior of this register.

#### 3.1.6 System Tick Compare Register (STICK\_CMPR)

Each strand has a privileged System Tick Compare (STICK\_CMPR) register, as described in the *UltraSPARC Architecture* 2005.

#### 3.1.7 PCR and PIC Registers

| ASR<br>Number    | ASR Name | Access | priv           | Replicated<br>by Strand | Description                                  |

|------------------|----------|--------|----------------|-------------------------|----------------------------------------------|

| 10 <sub>16</sub> | PCR      | RW     | Y <sup>2</sup> | Y                       | Performance counter control register         |

| 11 <sub>16</sub> | PIC      | RW     | $Y^1$          | Y                       | Performance Instrumentation Counter register |

TABLE 3-1

UltraSPARC T1-Specific Performance Instrumentation Registers

Notes:

1. Nonprivileged access with PCR.priv = 1 causes a *privileged\_action* exception.

2. Nonprivileged access causes a *privileged\_opcode* exception.

## 3.2 PR State Registers

#### 3.2.1 Trap State (TSTATE)

Each virtual processor (strand) has *MAXPTL*(2) Trap State (TSTATE) registers, as described in the *UltraSPARC Architecture* 2005.

#### 3.2.2 Processor State Register (PSTATE)

Each virtual processor (strand) has a Processor State register, as described in the *UltraSPARC Architecture* 2005.

#### 3.2.3 Trap Level Register (TL)

Each virtual processor (strand) has a Trap Level register, as described in the *UltraSPARC Architecture* 2005.

The maximum trap level (MAXPTL) for UltraSPARC T1 is 2.

#### 3.2.4 Global Level Register (GL)

Each virtual processor (strand) has a Global Level register, as described in the *UltraSPARC Architecture* 2005.

The maximum global level (MAXPGL) for UltraSPARC T1 is 2.

## 3.3 Floating-Point State Register (FSR)

Each virtual processor (strand) has a Floating-Point State register, **FSR**, as described in the *UltraSPARC Architecture* 2005.

UltraSPARC T1 does not provide a nonstandard floating-point mode, so the ns field of FSR is always 0.

On UltraSPARC T1, FSR.ver always reads as 0.

FSR.qne always reads as 0, because UltraSPARC T1 neither needs nor supports a floating-point queue (FQ).

## Instruction Set Overview

The UltraSPARC T1 processor implements the instruction set described in the *UltraSPARC Architecture* 2005. Additional UltraSPARC T1-specific details are described in this chapter.

## 4.1 State Register Access

UltraSPARC T1 supports the standard ASRs described in the *UltraSPARC Architecture* 2005.

## 4.2 Floating-Point Operate (FPop) Instructions

UltraSPARC T1 implements the floating-point instruction set described in the *UltraSPARC Architecture* 2005.

UltraSPARC T1 generates the correct IEEE Std 754-1985 results (impl. dep. #3).

All floating-point quad-precision operations cause an *fp\_exception\_other* trap with FSR.ftt = unimplemented\_FPop, and system software must emulate those operations.

## 4.3 Reserved Opcodes and Instruction Fields

An attempt to execute an opcode to which no instruction is assigned causes a trap. Specifically:

- Attempting to execute a reserved FPop causes an *fp\_exception\_other* trap (with FSR.ftt = unimplemented\_FPop).

- Attempting to execute any other reserved opcode causes an *illegal\_instruction* trap.

- Attempting to execute a Tcc instruction with a nonzero value in the reserved field (bits 10:8 and 6:5 when i = 0 or bits 10:7 when i = 1) causes an *illegal\_instruction* trap. See *Trap on Integer Condition Codes (Tcc)* on page 16.

See Appendix C, *Opcode Maps*, for a complete enumeration of the opcode assignments.

## 4.4 Register Window Management

*N\_REG\_WINDOWS* = 8 on UltraSPARC T1 (impl. dep. #2-V8). The state of the eight register windows is determined by the contents of the set of privileged registers described in the *UltraSPARC Architecture* 2005.

## Instruction Definitions

## 5.1 Instruction Set Summary

The UltraSPARC T1 CPU implements both the standard UltraSPARC Architecture 2005 instruction set and a number of implementation-dependent extended instructions. Standard UltraSPARC Architecture 2005 instructions are documented in the *UltraSPARC Architecture 2005*. UltraSPARC T1 extended instructions are documented <u>in VIS Instructions</u> on page 16.

The superscripts and their meanings are defined in TABLE 5-1.

| TABLE 5-1 | Instruction Superscripts |  |

|-----------|--------------------------|--|

|           |                          |  |

| Superscript | Meaning                |

|-------------|------------------------|

| D           | Deprecated instruction |

| Р           | Privileged instruction |

UltraSPARC T1 executes most UltraSPARC Architecture 2005 instructions in hardware. Those that trap and are emulated in software are listed in TABLE 5-2.

TABLE 5-2UltraSPARC Architecture 2005 Instructions Not Directly Implemented by UltraSPARC T1<br/>Hardware (1 of 3)

| Instruction         | Description                                                            | Exception Caused by<br>Attempted Execution |

|---------------------|------------------------------------------------------------------------|--------------------------------------------|

| ALLCLEAN            | Mark all windows as clean                                              | illegal_instruction                        |

| ARRAY{8,16,32}      | 3-D address to blocked byte address conversion                         | illegal_instruction                        |

| BMASK               | Write the GSR.mask field                                               | illegal_instruction                        |

| BSHUFFLE            | Permute bytes as specified by the GSR.mask field                       | illegal_instruction                        |

| EDGE{8,16,32}{L}{N} | Edge boundary processing {little-endian} {non-condition-code altering} | illegal_instruction                        |

| FABSq               | Floating-point absolute value quad                                     | fp_exception_other<br>[unimplemented_FPop] |

| Instruction   | Description                                                                                  | Exception Caused by<br>Attempted Execution |

|---------------|----------------------------------------------------------------------------------------------|--------------------------------------------|

| FADDq         | Floating-point add quad                                                                      | fp_exception_other<br>[unimplemented_FPop] |

| FCMPq         | Floating-point compare quad                                                                  | fp_exception_other<br>[unimplemented_FPop] |

| FCMPEq        | Floating-point compare quad (exception if unordered)                                         | fp_exception_other<br>[unimplemented_FPop] |

| FCMPEQ{16,32} | Four 16-bit / two 32-bit compare: set integer dest if src1 = src2                            | illegal_instruction                        |

| FCMPGT{16,32} | Four 16-bit / two 32-bit compare: set integer dest if src1 > src2                            | illegal_instruction                        |

| FCMPLE{16,32} | Four 16-bit / two 32-bit compare: set integer dest if src1 $\leq$ src2                       | illegal_instruction                        |

| FCMPNE{16,32} | Four 16-bit / two 32-bit compare: set integer dest if src1 $\neq$ src2                       | illegal_instruction                        |

| FDIVq         | Floating-point divide quad                                                                   | fp_exception_other<br>[unimplemented_FPop] |

| FdMULq        | Floating-point multiply double to quad                                                       | fp_exception_other<br>[unimplemented_FPop] |

| FEXPAND       | Four 8-bit to 16-bit expand                                                                  | illegal_instruction                        |

| FiTOq         | Convert integer to quad floating-point                                                       | fp_exception_other<br>[unimplemented_FPop] |

| FMOVq         | Floating-point move quad                                                                     | fp_exception_other<br>[unimplemented_FPop] |

| FMOVqcc       | Move quad floating-point register if condition is satisfied                                  | fp_exception_other<br>[unimplemented_FPop] |

| FMOVqr        | Move quad floating-point register if integer register contents satisfy condition             | fp_exception_other<br>[unimplemented_FPop] |

| FMULq         | Floating-point multiply quad                                                                 | fp_exception_other<br>[unimplemented_FPop] |

| FMUL8SUx16    | Signed upper 8- x 16-bit partitioned product of corresponding components                     | illegal_instruction                        |

| FMUL8ULx16    | Unsigned lower 8-bit x 16-bit partitioned product of corresponding components                | illegal_instruction                        |

| FMUL8x16      | 8- x 16-bit partitioned product of corresponding components                                  | illegal_instruction                        |

| FMUL8x16AL    | Signed lower 8-bit x 16-bit lower $\alpha$ partitioned product of four components            | illegal_instruction                        |

| FMUL8x16AU    | Signed upper 8-bit x 16-bit lower $\alpha$ partitioned product of four components            | illegal_instruction                        |

| FMULD8SUx16   | Signed upper 8-bit x 16-bit multiply $\leftarrow$ 32-bit partitioned product of components   | illegal_instruction                        |

| FMULD8ULx16   | Unsigned lower 8-bit x 16-bit multiply $\leftarrow$ 32-bit partitioned product of components | illegal_instruction                        |

| FNEGq         | Floating-point negate quad                                                                   | fp_exception_other<br>[unimplemented_FPop] |

## **TABLE 5-2**UltraSPARC Architecture 2005 Instructions Not Directly Implemented by UltraSPARC T1<br/>Hardware (2 of 3)

| Instruction             | Description                                                                            | Exception Caused by<br>Attempted Execution |

|-------------------------|----------------------------------------------------------------------------------------|--------------------------------------------|

| FPACKFIX                | Two 32-bit to 16-bit fixed pack                                                        | illegal_instruction                        |

| FPACK{16,32}            | Four 16-bit/two 32-bit pixel pack                                                      | illegal_instruction                        |

| FPMERGE                 | Two 32-bit to 64-bit fixed merge                                                       | illegal_instruction                        |

| FSQRT(s,d,q)            | Floating-point square root                                                             | fp_exception_other<br>[unimplemented_FPop] |

| F(s,d,q)TO(q)           | Convert between floating-point formats to quad                                         | fp_exception_other<br>[unimplemented_FPop] |

| FqTOi                   | Convert quad floating point to integer                                                 | fp_exception_other<br>[unimplemented_FPop] |

| FqTOx                   | Convert quad floating point to 64-bit integer                                          | fp_exception_other<br>[unimplemented_FPop] |

| FSUBq                   | Floating-point subtract quad                                                           | fp_exception_other<br>[unimplemented_FPop] |

| FxTOq                   | Convert 64-bit integer to floating-point                                               | fp_exception_other<br>[unimplemented_FPop] |

| IMPDEP1                 | Implementation-dependent instruction                                                   | illegal_instruction                        |

| IMPDEP2                 | Implementation-dependent instruction                                                   | illegal_instruction                        |

| INVALW <sup>P</sup>     | Mark all windows as CANSAVE                                                            | illegal_instruction                        |

| LDQF                    | Load quad floating-point                                                               | illegal_instruction                        |

| LDQFA                   | Load quad floating-point into alternate space                                          | illegal_instruction                        |

| LDSHORTF                | Short FP load, zero-extend 8/16-bit load to a double-precision floating-point register | data_access_exception                      |

| NORMALW                 | Mark other windows as restorable                                                       | illegal_instruction                        |

| OTHERW                  | Mark restorable windows as other                                                       | illegal_instruction                        |

| PDIST                   | Distance between eight 8-bit components                                                | illegal_instruction                        |

| POPC                    | Population count                                                                       | illegal_instruction                        |

| PST                     | Eight 8-bit/four 16-bit/two 32-bit partial stores                                      | data_access_exception                      |

| SHUTDOWN <sup>D,P</sup> | Shut down                                                                              | illegal_instruction                        |

| STBLOCKF                | 64-byte block store with commit                                                        | data_access_exception                      |

| STQF                    | Store quad floating-point                                                              | illegal_instruction                        |

| STQFA                   | Store quad floating-point into alternate space                                         | illegal_instruction                        |

| STSHORTF                | Short FP store, 8-/16-bit store from a double-precision floating-point register        | data_access_exception                      |

TABLE 5-2UltraSPARC Architecture 2005 Instructions Not Directly Implemented by UltraSPARC T1<br/>Hardware (3 of 3)

# 5.2 Prefetch and Prefetch from Alternate Space

PREFETCH and PREFETCHA with fcn codes of 0–3 and 16–23 ( $10_{16}$ –17<sub>16</sub>) are implemented; all map to the same operation that brings the cache line into the L2 cache. On an MMU miss, the prefetch is dropped (weak prefetching).

Prefetch for codes  $5_{16}$ - $F_{16}$  cause an *illegal\_instruction* trap. These operations are all "weak" prefetches; in some cases the prefetch operation is dropped.

## 5.3 Trap on Integer Condition Codes (Tcc)

See the *UltraSPARC Architecture* 2005 for a complete description of the Tcc instruction.

UltraSPARC T1For the i = 0 variant of Tcc, UltraSPARC T1 does not check thatImplementationreserved instruction bit 7 is 0. If bit 7 is set to 1 with i = 0,NoteUltraSPARC T1 treats it as a valid Tcc instruction.

## 5.4 VIS Instructions

UltraSPARC T1 supports in hardware the VIS 2 SIAM instruction and a subset of the VIS 1 instructions.

All other VIS 1 and VIS 2 instructions (see TABLE 5-2 for a list) cause an *illegal\_instruction* exception on UltraSPARC T1 and are emulated in software.

UltraSPARC T1<br/>Programming<br/>NoteThe use of VIS instructions on UltraSPARC T1 is strongly<br/>discouraged; the performance of even the implemented VIS<br/>instructions will often be below that of a comparable set of non-<br/>VIS instructions. This includes the block load and block store<br/>instructions. An UltraSPARC T1 physical processor core (four<br/>virtual processors) can only have a single outstanding floating-<br/>point operation (including block load, block store, and VIS<br/>instructions) in progress at any given time.

## 5.5 Partitioned Add/Subtract Instructions

See the *UltraSPARC Architecture* 2005 for detailed descriptions of the FPADD and FPSUB instructions.

UltraSPARC T1For good performance on UltraSPARC T1, the result of a singleProgrammingFPADD should not be used as part of a 64-bit graphicsNoteinstruction source operand in the next instruction group.

Similarly, the result of a standard FPADD should not be used as a 32-bit graphics instruction source operand in the next instruction group.

## 5.6 Align Data

See the *UltraSPARC Architecture* 2005 for detailed descriptions of the FALIGNDATA instruction.

UltraSPARC T1For good performance on UltraSPARC T1, the result ofProgrammingFALIGNDATA should not be used as the source operand of a 32-<br/>bit SIMD instruction in the next instruction group.

## 5.7 **F** Register Logical Operate Instructions

See the *UltraSPARC Architecture* 2005 for a description of the F register logical operate instructions (1-, 2-, and 3-operand).

UltraSPARC T1<br/>Programming<br/>NoteFor good performance on UltraSPARC T1, the result of a single<br/>logical operate instruction should not be used as part of the<br/>source operand of a 64-bit SIMD instruction in the next<br/>instruction group.

Similarly, the result of a standard logical operate instruction should not be used as the source operand of a 32-bit SIMD instruction source operand in the next instruction group.

## 5.8 Block Load and Store Instructions

For architectural descriptions of the LDBLOCKF and STBLOCKF instructions, see the *UltraSPARC Architecture* 2005.

| UltraSPARC T1<br>Implementation<br>Note |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Compatibility                           | These instructions were intended for use in transferring large                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Note                                    | blocks of data (more than 256 bytes); for example, in BCOPY and BFILL operations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                         | The use of block loads and stores on UltraSPARC T1 is deprecated; they are provided primarily for compatibility with existing software. UltraSPARC T1 provides a separate set of ASIs for high performance BCOPY and BFILL, as described in TABLE 9-1 on page 41. The performance of parallel BCOPY using appropriate ASIs (from among $22_{16}$ , $23_{16}$ , $E2_{16}$ , $E3_{16}$ , $EA_{16}$ , and $EB_{16}$ ) will be 2.5 to 3.5 times that of a BCOPY using block loads and stores. The performance of a single-threaded BCOPY using these ASIs will be 15% to 50% better than that of a BCOPY using block loads and stores. |

On UltraSPARC T1, to order an LDBLOCKF with respect to earlier stores, an intervening MEMBAR #Sync must be executed.

Similarly on UltraSPARC T1, STBLOCKF source data registers are not interlocked against completion of previous load instructions (even if a second LDBLOCKF has been performed). The previous load data must be referenced by some other intervening instruction, or an intervening MEMBAR #Sync must be performed. If the programmer violates these rules, data from before or after the load may be used. UltraSPARC T1 continues execution before all of the store data has been transferred. If store data registers are overwritten before the next block store or MEMBAR #Sync instruction, then the following rule must be observed. The first register can be overwritten in the same instruction group as the STBLOCKF, the second register can be overwritten in the instruction group following the block store and so on. If this rule is violated, the store may store correct data or the overwritten data. Block stores always operate under the relaxed memory order (RMO) memory model, regardless of the PSTATE.mm setting, and require a subsequent MEMBAR #Sync to order them with respect to following loads.

After an STBLOCKF instruction but before executing a DONE, RETRY, or WRPR to PSTATE instruction, there must be an intervening MEMBAR #Sync or a trap. If this is rule is violated, instructions after the DONE, RETRY, or WRPR to PSTATE may not see the effects of the updated PSTATE.

On UltraSPARC T1, LDBLOCKF does not follow memory model ordering with respect to stores. In particular, read-after-write and write-after-read hazards to overlapping addresses are not detected. The side-effects bit associated with the access is ignored (see *Translation Table Entry (TTE)* on page 53). If ordering with respect to earlier stores is important (for example, a block load that overlaps previous stores), then there must be an intervening MEMBAR #StoreLoad (or stronger MEMBAR). If ordering with respect to later stores is important (for example, a block load that overlaps a subsequent store), then there must be an intervening MEMBAR #LoadStore or reference to the block load data. This restriction does not apply when a trap is taken, so the trap handler need not consider pending block loads. If the LDBLOCKF overlaps a previous or later store and there is no intervening MEMBAR, trap, or data reference, the LDBLOCKF may return data from before or after the store.

**Compatibility** Prior UltraSPARC machines may have written loaded data into the first two registers at the same time. Software that depends on this unsupported behavior must be modified for UltraSPARC T1.

STBLOCKF does not follow memory model ordering with respect to loads, stores or flushes. In particular, read-after-write, write-after-write, flush-after-write, and writeafter-read hazards to overlapping addresses are not detected. The side-effects bit associated with the access is ignored. If ordering with respect to earlier or later loads or stores is important, then there must be an intervening reference to the load data (for earlier loads), or appropriate MEMBAR instruction. This restriction does not apply when a trap is taken, so the trap handler does not have to worry about pending block stores. If the STBLOCKF overlaps a previous load and there is no intervening load data reference or MEMBAR #LoadStore instruction, the load may return data from before or after the store and the contents of the block are undefined. If the STBLOCKF overlaps a later load and there is no intervening trap or MEMBAR #StoreLoad instruction, the contents of the block are undefined. If the STBLOCKF overlaps a later store or flush and there is no intervening trap or MEMBAR #StoreStore instruction, the contents of the block are undefined. If the STBLOCKF overlaps a later store or flush and there is no intervening trap or MEMBAR #StoreStore instruction, the contents of the block are undefined.

Block load and store operations do not obey the ordering restrictions of the currently selected virtual processor memory model (always TSO in UltraSPARC T1); block operations always execute under an RMO memory ordering model. Explicit MEMBAR instructions are required to order block operations among themselves or with respect to normal loads and stores. In addition, block operations do not conform to dependence order on the issuing strand; that is, no read-after-write or writer-after-read checking occurs between block loads and stores. Explicit MEMBARs must be used to enforce dependence ordering between block operations that reference the same address.

Typically, LDBLOCKF and STBLOCKF are used in loops where software can ensure that there is no overlap between the data being loaded and the data being stored. The loop must be preceded and followed by the appropriate MEMBARs to ensure that there are no hazards with loads and stores outside the loops. CODE EXAMPLE 5-1 illustrates the inner loop of a byte-aligned block copy operation.

Note that the loop must be unrolled twice to achieve maximum performance. All FP register references in this code example are to 64-bit registers. Eight versions of this loop are needed to handle all the cases of double word misalignment between the source and destination.

| loon           |                                     |

|----------------|-------------------------------------|

| loop:          | %f0, %f2, %f34                      |

|                | %10, %12, %134<br>%f2, %f4, %f36    |

| 5              | %12, %14, %130<br>%f4, %f6, %f38    |

|                |                                     |

|                | %f6, %f8, %f40                      |

| 5              | %f8, %f10, %f42                     |

|                | %f10, %f12, %f44                    |

|                | %f12, %f14, %f46                    |

|                | %10, -1, %10                        |

| bg,pt          | 11                                  |

| fmovd          |                                     |

|                | p handling                          |

|                | [regaddr] #ASI_BLK_P, %f0           |

| stda           | %f32, [ <i>regaddr</i> ] #ASI_BLK_P |

|                | %f48, %f16, %f32                    |

|                | %f16, %f18, %f34                    |

|                | %f18, %f20, %f36                    |

|                | %f20, %f22, %f38                    |

|                | %f22, %f24, %f40                    |

|                | %f24, %f26, %f42                    |

|                | %f26, %f28, %f44                    |

| 5              | %f28, %f30, %f46                    |

| addcc          | %10, -1, %10                        |

| be,pnt         |                                     |

| fmovd          | %f30, %f48                          |

| ldda           | [ <i>regaddr</i> ] #ASI_BLK_P, %f16 |

| stda           | %f32, [ <i>regaddr</i> ] #ASI_BLK_P |

| ba             | loop                                |

| faligndata     | %f48, %f0, %f32                     |

| done: end of I | loop processing                     |

|                |                                     |

CODE EXAMPLE 5-1 Byte-Aligned Block Copy Inner Loop

## 5.9 Block Initializing Store ASIs

The Block Initializing Store ASIs are specific to the UltraSPARC T1 implementation and are not guaranteed to be portable to other UltraSPARC Architecture implementations. They should only appear in platform-specific dynamically-linked libraries or in code generated at runtime by software (for example, a just-in-time compiler) that is aware of the specific implementation upon which it is executing.

| Instruction    | imm_asi          | ASI<br>Value     | Operation                                                                                      | Assembly Language Syntax                                                                                                                            |

|----------------|------------------|------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| ST{B,H,W,X,D}A | ASI_STBI_AIUP    | 22 <sub>16</sub> | 64-byte block initialing store<br>to primary address space,<br>user privilege                  | est{b,h,w,x,d}a <i>reg<sub>rd</sub>,</i> [ <i>reg_addr</i> ] <i>imm_asi</i><br>st{b,h,w,x,d}a <i>reg<sub>rd</sub>,</i> [ <i>reg_plus_imm</i> ] %asi |

| ST{B,H,W,X,D}A | ASI_STBI_AIUS    | 23 <sub>16</sub> | 64-byte block initialing store<br>to secondary address space,<br>user privilege                |                                                                                                                                                     |

| ST{B,H,W,X,D}A | ASI_STBI_N       | 27 <sub>16</sub> | 64-byte block initialing store<br>to nucleus address space                                     |                                                                                                                                                     |

| ST{B,H,W,X,D}A | ASI_STBI_AIUPL_L | 2A <sub>16</sub> | 64-byte block initialing store<br>to primary address space,<br>user privilege, little-endian   |                                                                                                                                                     |

| ST{B,H,W,X,D}A | ASI_STBI_AIUSL   | 2B <sub>16</sub> | 64-byte block initialing store<br>to secondary address space,<br>user privilege, little-endian |                                                                                                                                                     |

| ST{B,H,W,X,D}A | ASI_STBI_NL      | 2F <sub>16</sub> | 64-byte block initialing store<br>to nucleus address space,<br>little-endian                   |                                                                                                                                                     |

| ST{B,H,W,X,D}A | ASI_STBI_P       | E2 <sub>16</sub> | 64-byte block initialing store<br>to primary address space                                     |                                                                                                                                                     |

| ST{B,H,W,X,D}A | ASI_STBI_S       | E3 <sub>16</sub> | 64-byte block initialing store<br>to secondary address space                                   |                                                                                                                                                     |

| ST{B,H,W,X,D}A | ASI_STBI_PL      | EA <sub>16</sub> | 64-byte block initialing store<br>to primary address space,<br>little-endian                   | 2                                                                                                                                                   |

| ST{B,H,W,X,D}A | ASI_STBI_SL      | EB <sub>16</sub> | 64-byte block initialing store<br>to secondary address space,<br>little-endian                 |                                                                                                                                                     |

Description The UltraSPARC T1-specific block initializing store instructions are selected by using one of the block-initializing ASIs with integer store alternate instructions. These ASIs allow block-initializing stores to be performed to the same address spaces as normal stores. Little-endian ASIs access data in little-endian format; otherwise, the access is assumed to be big-endian.

Integer stores of all sizes are allowed with these ASIs, and STDA behaves as a standard store doubleword. All stores to these ASIs operate under relaxed memory ordering (RMO), regardless of the value of PSTATE.mm. Software must follow a sequence of these stores with a MEMBAR #Sync to ensure ordering with respect to subsequent loads and stores.

A store to one of these ASIs where the least-significant 6 bits of the address are nonzero (that is, not the first word in the cache line) behaves the same as a normal store (with RMO ordering).

A store to one of these ASIs where the least-significant 6 bits of the address are zero will load a cache line in the L2 cache with either all zeros or the existing memory data, and then update the beginning of the cache line with the new store data. This special store behavior ensures that the line maintains coherency when it is loaded into the cache, but will not generally fetch the line from memory (instead, initializing it with zeroes).

A store using one of these ASIs to a noncacheable location behaves the same as a normal store.

UltraSPARC T1 | On UltraSPARC T1, a noncacheable address is identified by . Implementation Note

Programming<br/>NoteThese instructions are particularly useful in combination with<br/>load twin extended word instructions for transferring large<br/>blocks (more than 256 bytes) of data; for example, in<br/>implementing bcopy() and bfill() operations.

## UltraSPARC T1 | On UltraSPARC T1, block initializing stores and load twin doublewords from multiple strands are fully overlapped.

Attempted use of any of these ASIs by a floating-point store alternate instruction (STFA, STDFA) causes a *data\_access\_exception* exception.

Access to any of these ASIs by an instruction with misaligned address causes a *mem\_address\_not\_aligned* exception.

Programming<br/>NoteThe following pseudocode shows how these ASIs can be used to<br/>do a quadword-aligned (on both source and destination) copy of<br/>N quadwords from A to B (where N > 3). Note that the final 64<br/>bytes of the copy is performed using normal stores, to guarantee<br/>that all initial zeros in a cache line are overwritten with copy<br/>data.

```

10 \leftarrow [A]; 11 \leftarrow [B]

prefetch [%10]

for (i = 0; i < N-4; i++) {

if (!(i % 4)) { prefetch [%10+64] }

ldda [%l0] #ASI_BLK_INIT_ST_P, %l2

add %10, 16, %10

stxa %12, [%11] #ASI_BLK_INIT_ST_P

add %11, 8, %11

stxa %13, [%11+8] #ASI_BLK_INIT_ST_P

add %11, 8, %11

for (i = 0; i < 4; i++) {

ldda [%10] #ASI_BLK_INIT_ST_P, %12

add %10, 16, %10

stx %12, [%11]

stx %13, [%11+8]

add %11, 16, %11

}

membar #Sync

```

An overlapped copy operation must avoid issuing a block-init store to a line before all loads from that line have been issued. Otherwise, one or more of the loads may see the interim "zero" side-effect value. This typically means that **abs**(A–B) must be 64.

| (1) These ASIs are specific to UltraSPARC T1, to provide a high-<br>performance mechanism for BCOPY operations, as an<br>alternative to legacy block load and block store instructions<br>(which rely on the floating-point register file and thus are<br>limited by the single register file port). These ASIs are only                                                                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| allowed in platform-specific dynamically linked libararies and<br>in code generated at runtime by software (for example, a just-in-<br>time compiler) that is aware of the implementation upon which<br>it is executing.                                                                                                                                                                                                                                                                                                                                                   |

| (2) These ASIs provide a higher performance bcopy() or bfill() than the block loads and stores described in Section 5.8, due to their ability to overlap multiple loads and stores between strands and to avoid the unnecessary fetch from memory of the data that is overwritten by the store. The performance of parallel bcopy() using these ASIs will be 2.5 to 3.5 times that of a bcopy() using block loads and stores. The performance of a single-threaded bcopy() using these ASIs will be 15% to 50% better than that of a bcopy() using block loads and stores. |

*Exceptions* VA\_watchpoint mem\_address\_not\_aligned data\_access\_exception

# 5.10 Load Twin Extended Word Instructions (nonprivileged)

The Load Twin Extended Word Instructions are not guaranteed to be portable to other UltraSPARC Architecture implementations. They should only appear in platform-specific dynamically-linked libraries or in code generated at runtime by software (for example, a just-in-time compiler) that is aware of the specific implementation upon which it is executing.

*Description* Load Twin Extended Word instructions are new in the UltraSPARC Architecture 2005; they are used to atomically read a 128-bit data item into a pair of integer registers.

See the UltraSPARC Architecture 2005 for details.

- Programming<br/>NoteThese instructions are particularly useful in combination with<br/>block-initializing stores for transferring large blocks of data<br/>(more than 256 bytes); for example, in implementing bcopy()<br/>and bfill() operations. See the description of Block Initializing<br/>Stores for an example of how Load Twin Extended Word can be<br/>used in combination with those instructions.

- UltraSPARC T1<br/>Implementation<br/>NoteOn UltraSPARC T1, a load twin extended word forces a miss in<br/>the primary cache and will *not* allocate a line in the primary<br/>cache, but does allocate in L2. On UltraSPARC T1, block<br/>initializing stores and load twin doublewords from multiple<br/>strands are fully overlapped.

See the description of Block Initializing Stores for an example of how Load Twin Doubleword can be used in combination with those instructions.

| UltraSPARC T1 | (1) These instructions, combined with store instructions using      |

|---------------|---------------------------------------------------------------------|

| Programming   | the UltraSPARC T1-specific Block Initializing Store ASIs,           |

| Notes         | provide a high-performance mechanism for BCOPY operations,          |

|               | as an alternative to legacy block load and store (which rely on     |

|               | the floating-point register file and thus are limited by the single |

|               | register file port). These ASIs are only allowed in platform-       |

|               | specific dynamically linked libararies and in code generated at     |

|               | runtime by software (for example, a just-in-time compiler) that     |

|               | is aware of the implementation upon which it is executing.          |

|               |                                                                     |

|               | (2) These ASIs provide a higher performance bcopy() or              |

|               | bfill() than the block loads and stores described in                |

|               | Section 5.8, due to their ability to overlap multiple loads and     |

|               | stores between strands and to avoid the unnecessary fetch from      |

|               | memory of the data that is overwritten by the store. The            |

|               | performance of parallel bcopy() using these ASIs will be 2.5 to     |

|               | 3.5 times that of a bcopy() using block loads and stores. The       |

|               | performance of a single-threaded bcopy() using these ASIs will      |

|               | be 15% to 50% better than that of a bcopy() using block loads       |

|               | and stores.                                                         |

|               |                                                                     |

*See Also* Block Initializing Store ASIs on page 21.

# 5.11 Load Twin Extended Word Instructions (privileged)

| Instruction | imm_asi         | ASI<br>Value       | Operation                                                                            | Assembly L | anguage Syntax                                                                    |

|-------------|-----------------|--------------------|--------------------------------------------------------------------------------------|------------|-----------------------------------------------------------------------------------|

| LDTX        | ASI_LDTX_N      | 27 <sub>16</sub> † | 128-bit atomic load                                                                  |            | g_addr] <b>imm_asi</b> , reg <sub>rd</sub><br>g_plus_imm] %asi, reg <sub>rd</sub> |

| LDTX        | ASI_LDTX_REAL   | 26 <sub>16</sub>   | 128-bit atomic load, real<br>addressing (RA{63:0} set to<br>VA{63:0})                |            |                                                                                   |

| LDTX        | ASI_LDTX_NL     | 2F <sub>16</sub> ‡ | 128-bit atomic load, little<br>endian                                                |            |                                                                                   |

| LDTX        | ASI_LDTX_REAL_L | 2E <sub>16</sub>   | 128-bit atomic load, real<br>addressing (RA{63:0} set to<br>VA{63:0}), little endian |            |                                                                                   |

<sup>+</sup> ASI 24<sub>16</sub> (deprecated) is aliased to ASI 27<sub>16</sub> in UltraSPARC T1.

<sup>‡</sup> ASI  $2C_{16}$  (deprecated) is aliased to ASI  $2F_{16}$  in UltraSPARC T1.

| 11    | rd    | 01 0011 | rs1   | i=0 | imm_asi | rs2 |

|-------|-------|---------|-------|-----|---------|-----|

| 11    | rd    | 01 0011 | rs1   | i=1 | simm_13 |     |